電源ノイズの抑制とその対策

SSN解析にも耐えうるDDR実装設計、ジッター抑制によるタイミングマージン確保

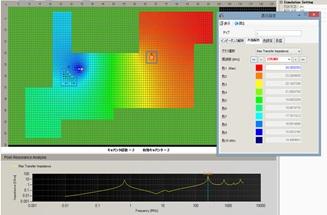

カスタマーの基板層構成に合わせたLSIのデカップ容量の配置推奨レイアウトの作成

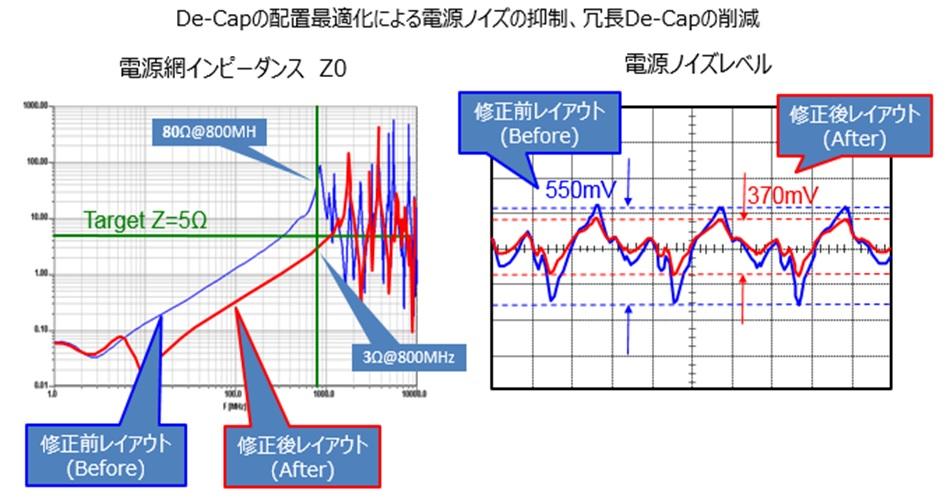

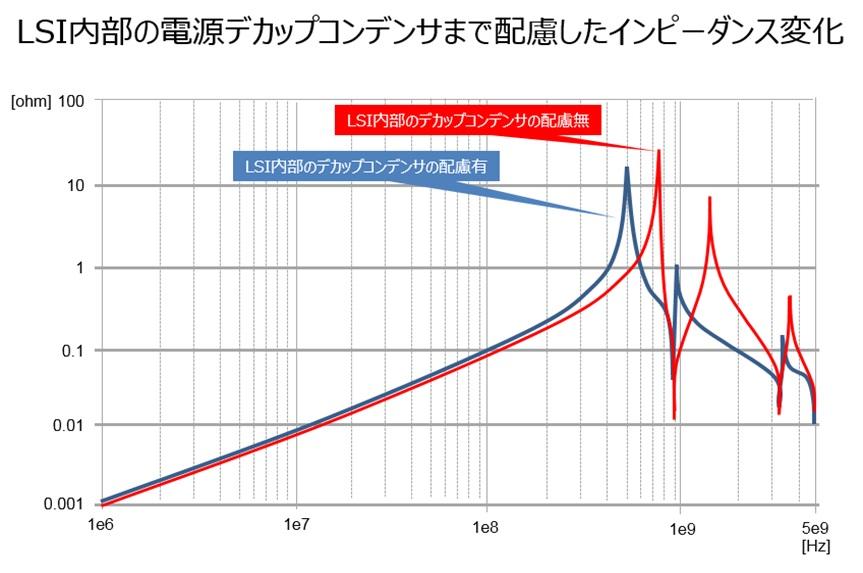

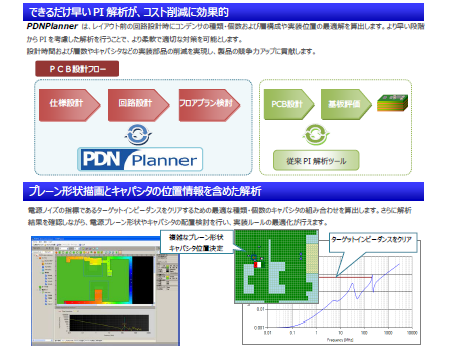

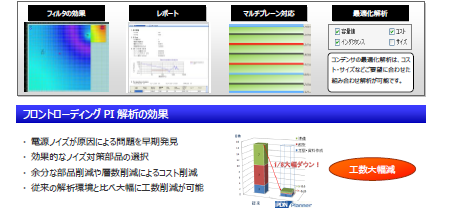

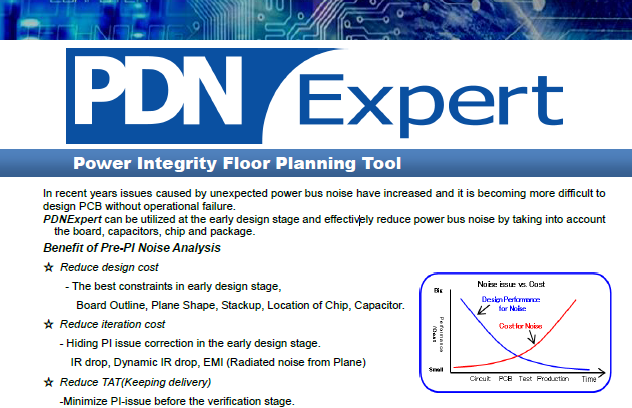

LSIや高速信号を安定的に動作させ、EMCの影響度を軽減する上で、電源の安定性は重要なポイントとなります。なぜならば、LSIや高速信号の駆動回路や受信回路の電源にノイズが発生すると、信号波形に歪や時間軸方向の揺らぎを発生させると共にLSI内部で発生した電源ノイズが基板上を伝播するからです。そのため、これら電源ノイズを抑制するために、パワーインテグリティ解析を用いた検証が広く用いられるようになりました。また、電源を安定化させるために用いられるデカップリングコンデンサは、過去の経験則等で置かれることが多く、冗長でノイズ抑制に効果的に効かないデカップコンデンサでもLSIの周辺近くに数多く実装される設計事例もあります。

一方、LSIベンダーからの電源パスコン配置指定が存在する場合でも、製品競争力の視点から、配置ルールを守れないケースも存在し、それでも理論的にリスクを低減できるデカップリングコンデンサの最適な配置方法をパワーインテグリティ解析によって導出し、極力コストを抑えることが求められるようになりました。また、DDRメモリのようなパラレルバスインターフェースにおいては、複数の信号が同時動作に伴う過渡電流によって大きな電源ノイズが発生するケースもあります。電源ノイズの影響によって、IOバッファの出力のタイミングが揺らぎ(ジッタ)が発生し、規定されるタイミングバジェットを守れなくなり誤動作が発生るする事もあります。更に高速シリアルバスにおいては、データのクロックを生成する上で重要なPLL電源にノイズが回りこむことでジッタが発生し、正常なデータ伝送が出来ない場合もあります。

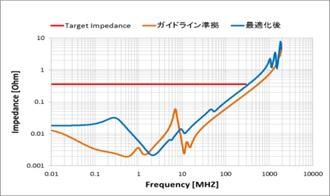

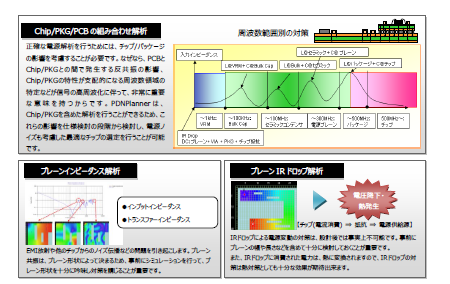

このような問題点を解決するために、弊社では自分自身のスイッチングによる電源の安定性を評価するためのインプットインピーダンス解析とノイズの回り込むを評価するためのトランスファーインピーダンス解析を組み合わせることで最適な電源設計方法を提案します。

- PIの指標となる基本パラメータ

・自身の電流印加(1A正弦波)による電圧変動

- PIだけでなくEMIにも関係するパラメータ

・励振点に電流印加した場合の、励振点以外の位置の電圧変動

・ノイズ源からEMI上のアンテナとなる箇所との間のカップリング特性を表す

・他のチップへのノイズ伝搬

パワーインテグリティ解析(電源zoの最適設計)

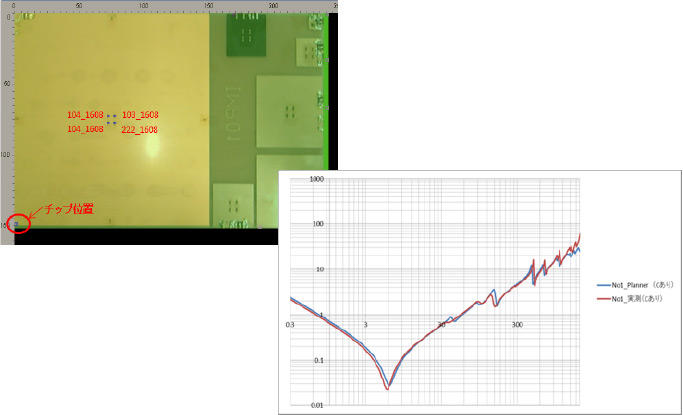

キャパシタ実装後の実測結果との比較

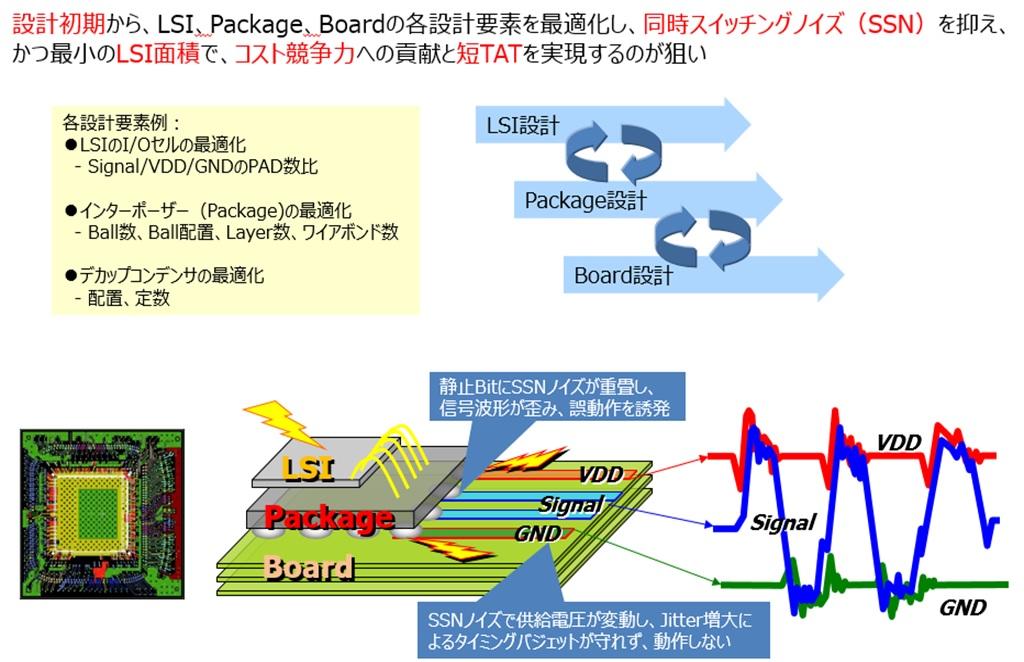

新規にLSIを開発する際に、最終製品側の基板や構造等からくるBall配置案と新規LSIとDieにおける各種フロアプラン(PAD配置)など、LSI(デバイス側)と最終製品側と協調しながら開発を進めます。設計初期から、LSI、パッケージ、基板の各設計要素を最適化すると共に、これらの3つの要素の相互作用を仮想モデルを用いて解析を行います。設計初期に設計課題を洗い出すことにより、低コストで設計改善を行うことを可能にすると共に、設計のやり直しのリスクを最小化します。

LSI/Package/Board協調設計

設計解析ソリューション統括部

TEL:045-474-9045